## Solutions - Quiz 1

(January 24th @ 5:30 pm)

## **PROBLEM 1 (30 PTS)**

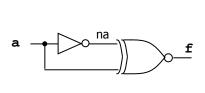

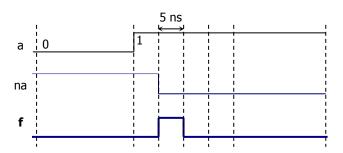

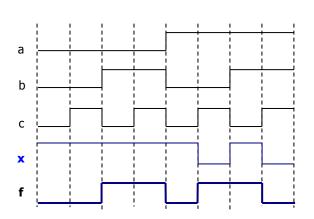

• Complete the timing diagram of the digital circuit shown below. You must consider the propagation delays. Assume the propagation delay of every gate is 5 ns. The initial values of all signals are plotted in the figure.

## **PROBLEM 2 (30 PTS)**

• Complete the timing diagram of the logic circuit whose VHDL description is shown below:

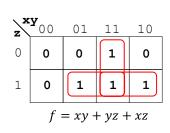

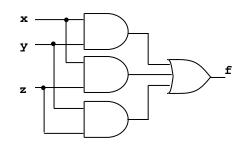

## PROBLEM 3 (40 PTS)

Design a 3-input circuit that generates a '0' when two or more of the inputs are '0'. It also generates a '1' when two or more

of the inputs are '1'. Complete the truth table, provide the simplified Boolean expression of the circuit, and sketch the

minimized circuit.

1

| x | У | Z | f |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |